How does the input output program works??

- CPU requests input output operation

- Input output module performs operation

- Input output module sets status operation

- CPU checks status bits periodically

- Input output module does not inform CPU directly

- Input output module does not interrupt CPU

- CPU may wait or come back later

Input Output Commands

- The processor issues and address, specifying input output module and device, and an input output command to execute the input output-related instruction. The commands are:

- Control - active a peripheral and tell it what to do

- Test - test various status conditions associated with an input output module and its peripherals

- Read - causes the input output module to obtain an item of data from the peripheral and place it into an internal register

- Write - causes the input output module to take a unit of data from the data bus and transmit it to the peripheral

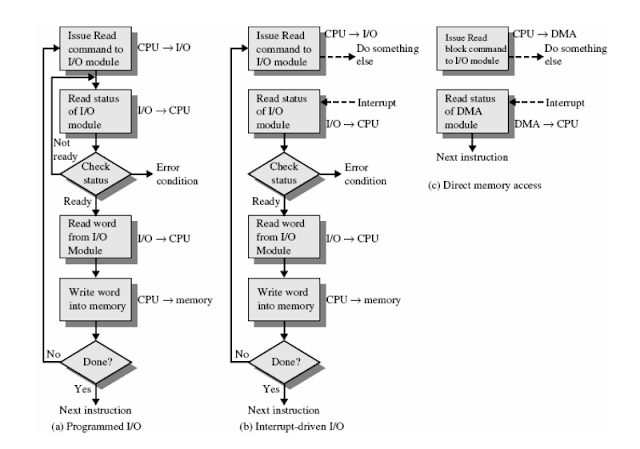

Three Techniques for Input of a Block of Data

Input Output Mapping

a. Memory-mapped Input Output

1. Single address space for both memory and input output device

* disadvantage - uses up valuable memory address space

2. Input output module treated as memory address

1. Single address space for both memory and input output device

* disadvantage - uses up valuable memory address space

2. Input output module treated as memory address

3. Same machine instruction used to access both memory and input

output devices

* advantages - allows for more efficient programming

4. Single read line and single write lines needed

5. Commonly used

b. Isolated Input Output

1. Separate address space for both memory and input output devices

2. Separate memory and input output select lines needed

3. Small number of input output instructions

4. Commonly used

5. INTERRUPT-DRIVEN INPUT OUTPUT

Purpose:

Input Output View Point

Interrupt Processing

Design Issues

a. Device identification

1. Multiple interrupt lines - each line may have multiple input output modules

2. Software poll - poll each input output module

DMA and Interrupt Breakpoints during Instruction Cycle

b. Isolated Input Output

1. Separate address space for both memory and input output devices

2. Separate memory and input output select lines needed

3. Small number of input output instructions

4. Commonly used

5. INTERRUPT-DRIVEN INPUT OUTPUT

Purpose:

- Overcome the processor having to wait long periods of time for input output modules

- The processor does not have to repeatedly check the input output module status

Input Output View Point

- input output receives a READ command from the processor

- input output reads data from desired peripheral into data register

- input output interrupts the processor

- input output waits until data is requested by the processor

- input output places data on the data bus when requested

Interrupt Processing

- The processor issues a READ command

- The processor performs some other useful work

- The processor checks for interrupts at the end of the instruction cycle

- The processor shaves the current context when interrupted by the input output module

- The processor read the data from the input output module and stores it in memory

- The processor then restores the saved content and resumes execution

a. Device identification

1. Multiple interrupt lines - each line may have multiple input output modules

2. Software poll - poll each input output module

- Separate command line - eg: TESTI/O

- Processor read status register of input output module

- Time consuming

- Hardware poll

- Common sends interrupt acknowledge

- Processor sends interrupt acknowledge

- Requesting input output module places a word of data on the data lines - "vector" that uniquely identifies the input output module - called vectored interrupt

- Input output first gains control of the bus

- Input output module sends interrupt request

- The processor acknowledge the interrupt request

- Input output places its vector of the data lines

Multiple Interrupts

1. Disable interrupts

- Processor will ignore further interrupts whilst processing one interrupt

- Interrupts remain pending and are checked after first interrupt has been processed

- Interrupts handled in sequence as they occur

- Low priority interrupts can be interrupted by higher priority interrupts

- When higher priority interrupt has been processed, processor returns to previous interrupt

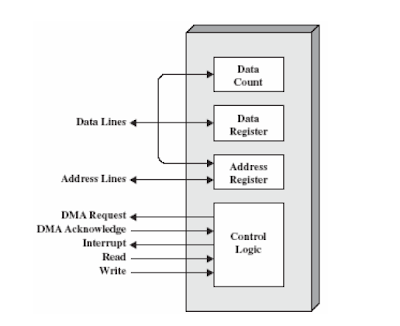

6. DIRECT MEMORY ACCESS (DMA)

DMA Function

- DMA module on system bus used to mimic the processor

- DMA module only uses system bus when processor does not need it

- DMA module may temporarily force processor to suspend operations - cycle stealing

DMA Operation

1. The processor issues a command to DMA module

- Read or write

- Input output device addressing using data lines

- Starting memory address using data lines - stored in address register

- Number of words to be transferred using data lines - stored in data register

2. The processor then continues with other work

3. DMA module transfers the entire block of data - one word at a time - directly to or from memory without going through the processor

4. DMA module sends an interrupt to the processor when complete

- The processor is suspended just before it needs to use the bus

- The DMA module transfers one word and returns control to the processor

- Since this is not an interrupt, the processor does not have to save context

- The processor executes more slowly, but this is still far more efficient that either programmed or interrupt-driven input output

DMA Configurations

- Single bus - detached DMA module

- Each transfers uses bus twice - input output to DMA, DMA to memory

- Processor suspended twice

- Single bus - integrated DMA module

- Module may support more than one device

- Each transfer uses bus once - DMA to memory

- Processor suspended once

- Separate input output bus

- Bus supports all DMA enabled devices

- Each transfer uses bus once - DMA to memory

- Processor suspended once

to be continued soon...

nadhiah amira nordin

<B031310415>

No comments:

Post a Comment